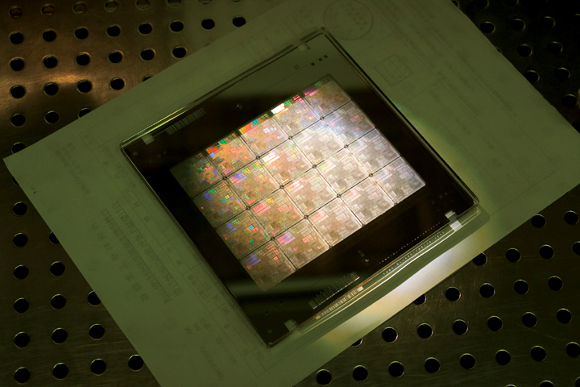

台湾のチップメーカーTSMCは、6nm(ナノメートル)プロセス(6N)を現地時間の16日付で発表しました。6nmプロセスのロジック密度は、7nmプロセスと比べて18%増となっています。

7nmプロセスとの互換性も確保

TSMCは先日、「N7 Pro」と呼ばれる極端紫外線リソグラフィ(EUV)を使用した7nmプロセスで次世代iPhoneのシステム・オン・チップA13を生産する見込みであると伝えられましたが、同社は新たに6nmプロセス(6N)を発表しました。

6Nのロジック密度は7nmプロセスと比較して18%増となっていますが、デザインルールは7nmプロセス(7N)と互換性が保証されており、前プロセスからの移行が容易になっています。

6Nプロセスでのリスク生産は2020年に予定されており、ハイエンドからミッドレンジのスマートフォン、人工知能(AI)5Gインフラ、GPUなどへの応用が期待されています。

「TSMCのN6技術は、N7を超える高パフォーマンスとコスト優位性で、プロダクト・ベネフィットにおいて業界を牽引していくだろう」と、TSMCのビジネス開発部門の上級副社長のケビン・チャン氏は述べています。

Source:TSMC

Photo:TSMC

(lexi)

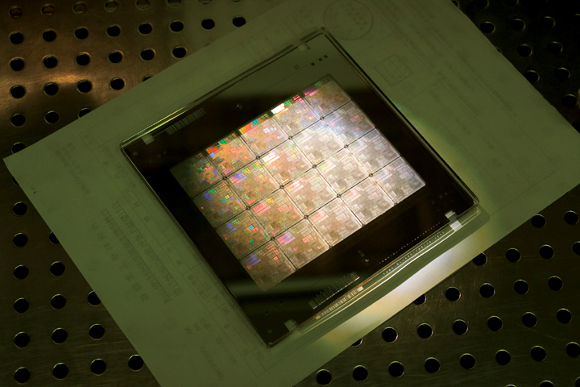

台湾のチップメーカーTSMCは、6nm(ナノメートル)プロセス(6N)を現地時間の16日付で発表しました。6nmプロセスのロジック密度は、7nmプロセスと比べて18%増となっています。

7nmプロセスとの互換性も確保

TSMCは先日、「N7 Pro」と呼ばれる極端紫外線リソグラフィ(EUV)を使用した7nmプロセスで次世代iPhoneのシステム・オン・チップA13を生産する見込みであると伝えられましたが、同社は新たに6nmプロセス(6N)を発表しました。

6Nのロジック密度は7nmプロセスと比較して18%増となっていますが、デザインルールは7nmプロセス(7N)と互換性が保証されており、前プロセスからの移行が容易になっています。

6Nプロセスでのリスク生産は2020年に予定されており、ハイエンドからミッドレンジのスマートフォン、人工知能(AI)5Gインフラ、GPUなどへの応用が期待されています。

「TSMCのN6技術は、N7を超える高パフォーマンスとコスト優位性で、プロダクト・ベネフィットにおいて業界を牽引していくだろう」と、TSMCのビジネス開発部門の上級副社長のケビン・チャン氏は述べています。

Source:TSMC

Photo:TSMC

(lexi)

コメント

コメントを投稿